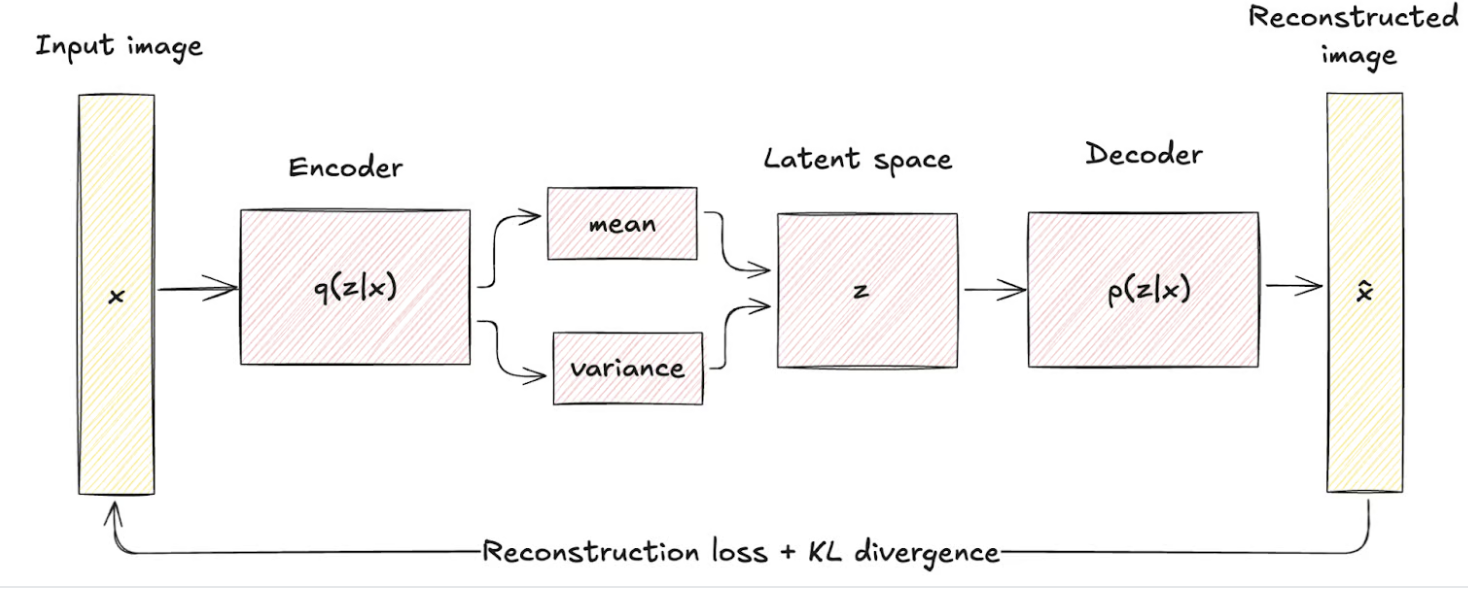

1. VAE의 개념- 입력 데이터를 압축한 뒤 다시 복원하는 과정에서 데이터의 잠재 공간을 학습하는 딥러닝 기반의 생성 모델활용) 이미지 생성, 이미지 스타일 변화, 이상치 탐지, 데이터 압축 2. VAE의 구성도 및 구성요소가. VAE 구성도 나. VAE 구성요소구분구성 요소설명Encoder- Input- 학습할 입력 데이터- Encoder- 입력 데이터 차원 축소 학습Latent Space- 평균, 분산- 입력 데이터 평균, 분산 생성- 잠재 변수- 평균, 분산 활용 잠재 변수 계산Decoder- Decoder- 잠재 변수 활용 원래 데이터 복원- Output- 복원된 출력 데이터Loss Function- Reconstruction Loss- 입력과 출력 데이터 비교- KL divergence- 잠..